THE MASKED GATE ARRAY ASIC An Application Specific Integrated Circuit or ASIC is a chip that can be designed by an engineer with no particular knowledge of semiconductor physics or semiconductor processes. To overcome the challenges yet realize the opportunities presented by semiconductor densities and capabilities electronic product companies utilize a System-on-a-Chip SoC design methodology which incorporates pre-designed components also called SoC Intellectual. asic and fpga design notes.

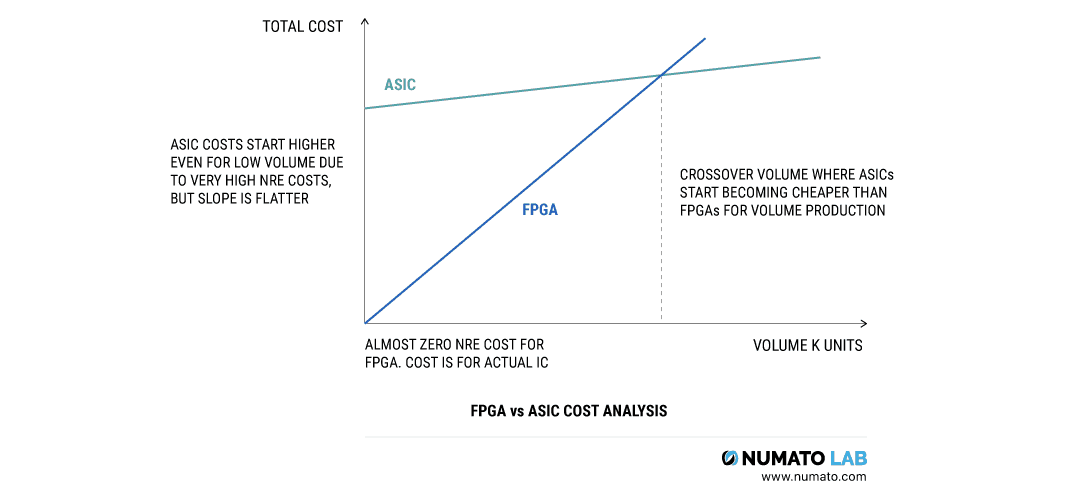

Asic And Fpga Design Notes, Starting ASIC development from scratch can cost well into millions of dollars. This lowers the cost and time required for many aspects of an FPGA. One can get started with FPGA development for as low as USD 30.

Fpga And Asic Technology Comparison Ppt Download From slideplayer.com

Fpga And Asic Technology Comparison Ppt Download From slideplayer.com

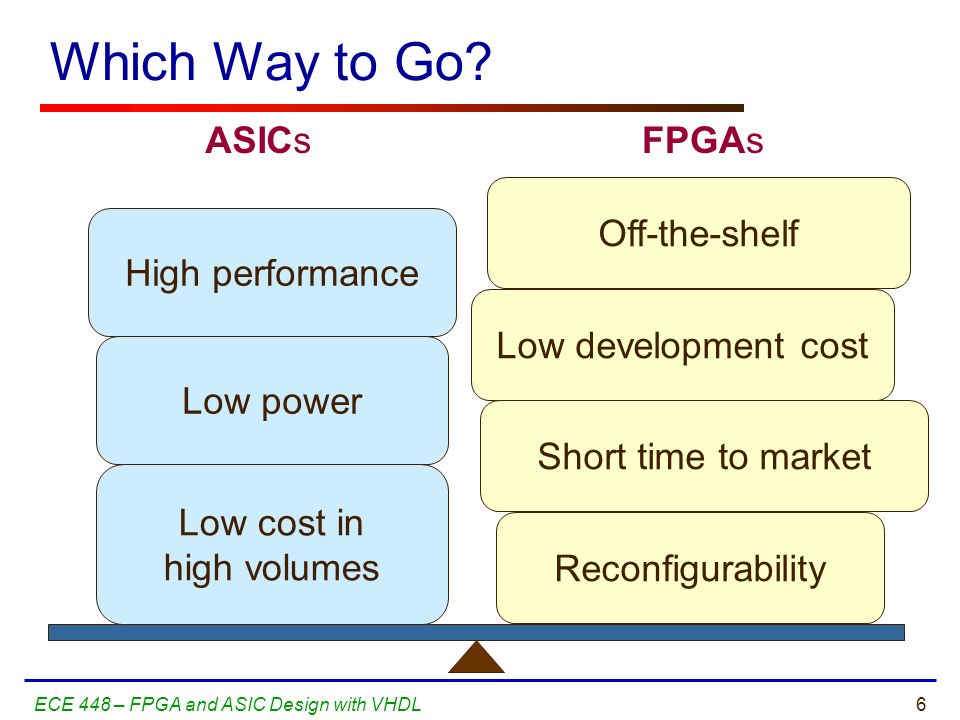

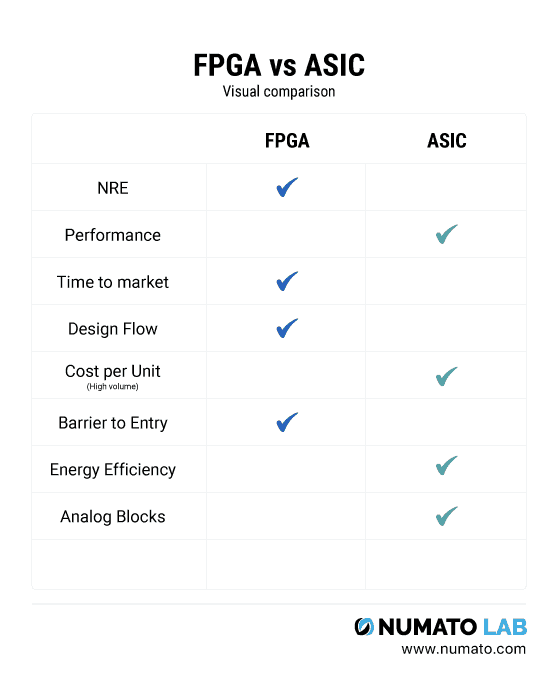

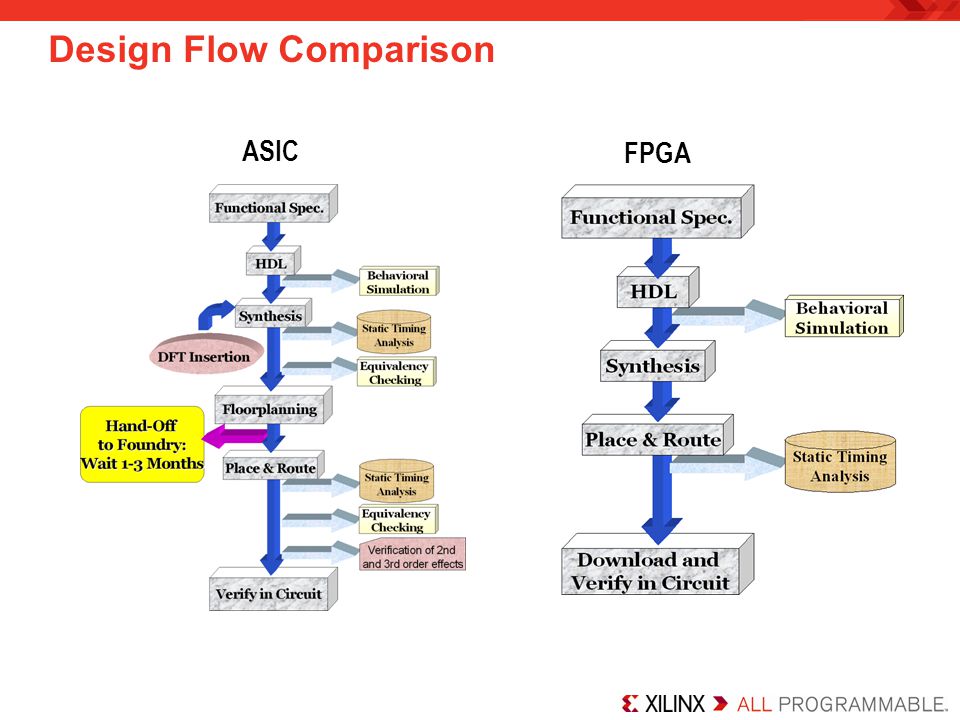

FPGA vs ASIC summary Front-end design flow is almost the same for both Back-end design flow optimization is different ASIC design. Freedom in routing gate sizing power gating and clock tree optimization. One can get started with FPGA development for as low as USD 30.

Introduction to ASIC specific design issues including.

Freedom in routing gate sizing power gating and clock tree optimization. FPGA vs ASIC summary Front-end design flow is almost the same for both Back-end design flow optimization is different ASIC design. This has been continuously driving the VLSI industry and the results of this law are the latest. THE MASKED GATE ARRAY ASIC An Application Specific Integrated Circuit or ASIC is a chip that can be designed by an engineer with no particular knowledge of semiconductor physics or semiconductor processes. Everything is preplaced clock tree is pre-routed no power gating Designs implemented in FPGAs are slower and. Generally an ASIC design will be undertaken for a product that will have a large production run and the ASIC may contain a very large part of the electronics needed on a single integrated circuit.

Another Article :

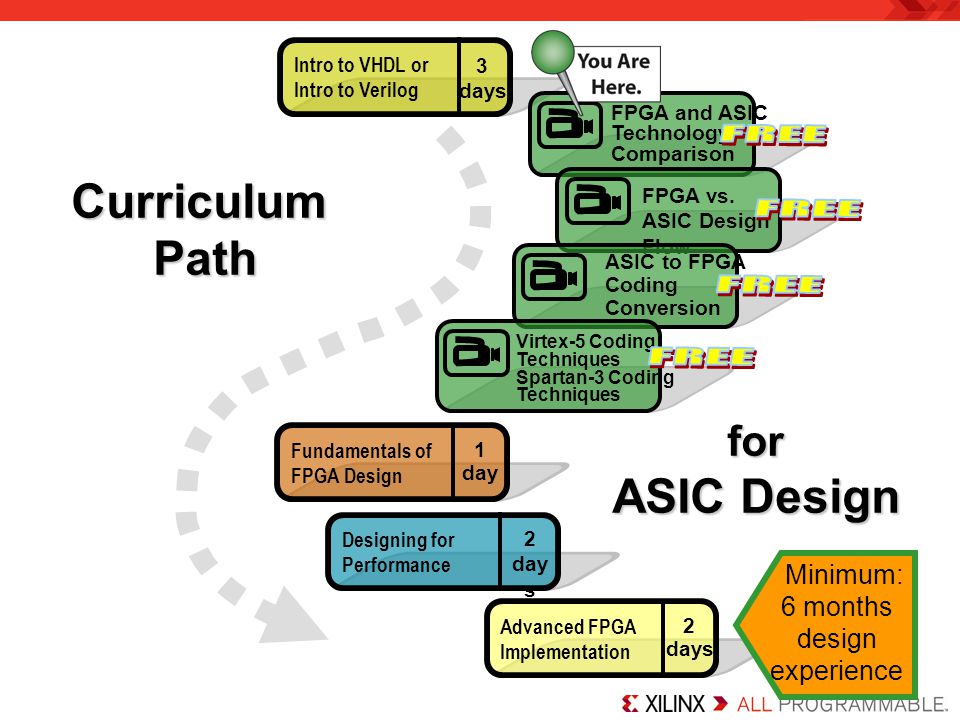

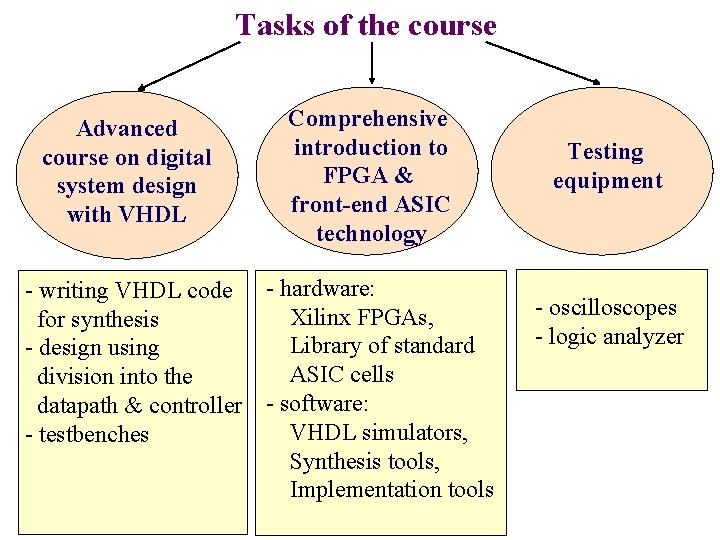

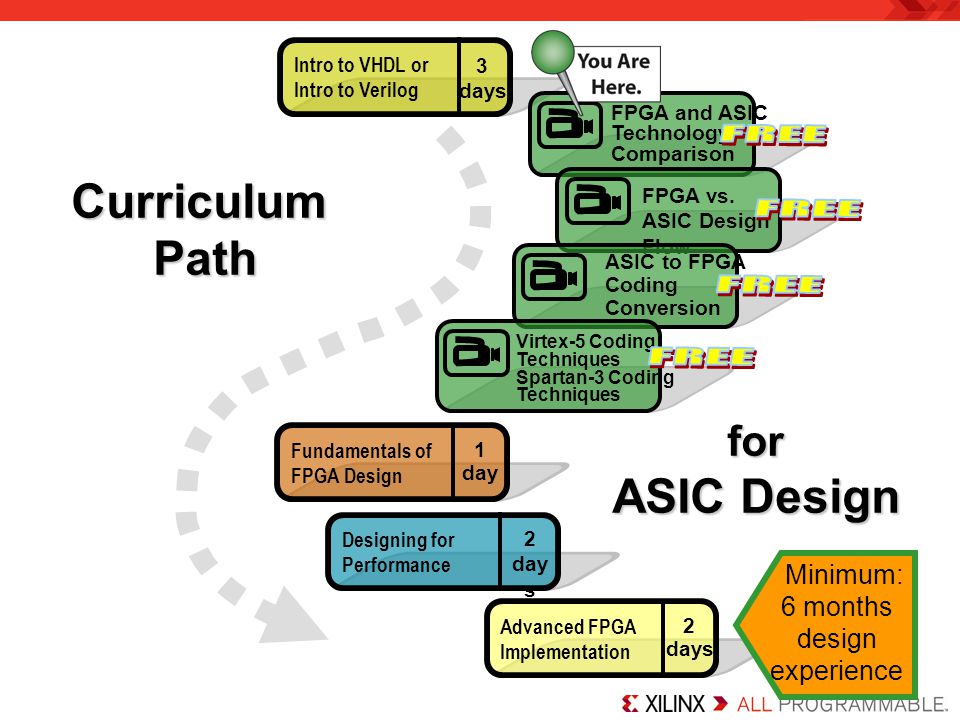

How to create fast and efficient FPGA designs by leveraging your ASIC design experience. FPGA synthesis tools will infer constructs that ASIC synthesis tools do not. Hardware Description Language HDL Verilog Professional Verilog Coding for Synthesis Verification Techniques FPGA Architectures Digital System Design with Xilinx FPGAs ASIC Digital Design Flow from Verilog to the actual Chip Synthesis Algorithms Power Dissipation Power Grid and Clock Design Fixed-point. The FPGA vendor on the other hand normally has no direct responsibility after delivering the unprogrammed devices. 3It is common practice to design and test on an FPGA before implementing on an ASIC. Ece 448 Fpga And Asic Design With Vhdl.

In addition to the non-recurring engineering NRE and mask costs development costs are increasing due to design complexity. The FPGA vendor on the other hand normally has no direct responsibility after delivering the unprogrammed devices. THE MASKED GATE ARRAY ASIC An Application Specific Integrated Circuit or ASIC is a chip that can be designed by an engineer with no particular knowledge of semiconductor physics or semiconductor processes. Even though an FPGA is a type of gate array we do not consider the term gate-array based ASICs to include FPGAs. Field-Programmable Gate ArraysFPGAs FPGAs are the newest member of the ASIC family and are rapidly growing in replacing TTL in microelectronic systems. Microsoft Fpga Vs Cpu Vs Asic Intel 10 Things Dedication.

Syllabus Regulation 2013 Click Here To Download. Everything is preplaced clock tree is pre-routed no power gating Designs implemented in FPGAs are slower and. FPGA flexibility and development benefits and ASIC size and power consumption advantages. 2-Marks Question with Answer University question paper MayJune 2016 University question paper NovDec2016 Notes Important Question for exam novdec 2016 Applied Electronics Syllabus Isem IIsem IIIsem. Design of digital application specific integrated circuits ASICs and Field Programmable Gate Arrays FPGAs based on hardware description languages Verilog and CAD tools. Fpga Devices Fpga Design Flow Ppt Download.

One can get started with FPGA development for as low as USD 30. This document is intended for traditional standard cell ASIC designers considering FPGA or HardCopy ASIC implementation of their designs either for prototyping or for production. Everything is preplaced clock tree is pre-routed no power gating Designs implemented in FPGAs are slower and. In view of the cost they are not used in cheap high volume products but instead FPGAs find applications in a variety of areas where complex logic circuitry may be needed and. Its now possible to achieve the best of both worlds with FPGA to ASIC conversion. Fpga Vs Asic Differences Between Them And Which One To Use Numato Lab Help Center.

Even though an FPGA is a type of gate array we do not consider the term gate-array based ASICs to include FPGAs. An FPGA synthesis tool will infer RAMs ROMs based on initial values or readmem. For more info visit. The significant difference between ASIC and FPGA design flow is that the design flow for ASICs is a far more complex and rigorous design-intensive process. 2An ASIC can no longer be altered once created while an FPGA can. Fpga And Asic Technology Comparison Ppt Download.

The ASIC vendor has created a library of cells and functions that the designer can use without needing to know precisely how. The significant difference between ASIC and FPGA design flow is that the design flow for ASICs is a far more complex and rigorous design-intensive process. When considering design cycle time note that the mask- programmable vendor has specific responsibilities in the ASIC design loop after completing each design. It will also help you fit your design into a smaller FPGA or a lower speed grade for reducing system costs. 1An ASIC is a unique type of integrated circuit meant for a specific application while an FPGA is a reprogrammable integrated circuit. Fpga Based Hardware Accelerators Lecture Notes In Electrical Engineering.

Same as for FPGA. An FPGA will require shallow combinatorial gate depth to get high speed ASIC is more forgiving. One can get started with FPGA development for as low as USD 30. AP7202 ASIC and FPGA Design Notes and Reference books. Generally an ASIC design will be undertaken for a product that will have a large production run and the ASIC may contain a very large part of the electronics needed on a single integrated circuit. Eetimes Asic Assp Soc Fpga What S The Difference.

In addition to the non-recurring engineering NRE and mask costs development costs are increasing due to design complexity. An FPGA synthesis tool will infer RAMs ROMs based on initial values or readmem. Freedom in routing gate sizing power gating and clock tree optimization. Same as for FPGA. FPGA synthesis tools will infer constructs that ASIC synthesis tools do not. Placement Vlsi Asic Fpga Embedded Pine Training Academy Training Academy Online Classes Analog Circuits.

This course will help you avoid the most common design mistakes of FPGA designers. Field-Programmable Gate ArraysFPGAs FPGAs are the newest member of the ASIC family and are rapidly growing in replacing TTL in microelectronic systems. Starting ASIC development from scratch can cost well into millions of dollars. When considering design cycle time note that the mask- programmable vendor has specific responsibilities in the ASIC design loop after completing each design. Everything is preplaced clock tree is pre-routed no power gating Designs implemented in FPGAs are slower and. Asic Vs Fpga Digital Design Analog Design Turnkey Asic Soc Embedded Firmware.

This application note gives some guidelines for efficient FPGA implementation of their designs. Very high entry-barrier in terms of cost learning curve liaising with semiconductor foundry etc. FPGA flexibility and development benefits and ASIC size and power consumption advantages. To overcome the challenges yet realize the opportunities presented by semiconductor densities and capabilities electronic product companies utilize a System-on-a-Chip SoC design methodology which incorporates pre-designed components also called SoC Intellectual. The FPGA vendor on the other hand normally has no direct responsibility after delivering the unprogrammed devices. Reality Tv For Fpga Design Engineers Edn.

Same as for FPGA. 2An ASIC can no longer be altered once created while an FPGA can. 2-Marks Question with Answer University question paper MayJune 2016 University question paper NovDec2016 Notes Important Question for exam novdec 2016 Applied Electronics Syllabus Isem IIsem IIIsem. To give the student an understanding of issues and tools related to ASICFPGA design and implementation including timing performance and power optimization verification and manufacturing test. This course will help you avoid the most common design mistakes of FPGA designers. Basics Of Core Based Fpga Design Part 4 Implementing A Design Embedded Com.

This document is intended for traditional standard cell ASIC designers considering FPGA or HardCopy ASIC implementation of their designs either for prototyping or for production. FPGA vs ASIC summary Front-end design flow is almost the same for both Back-end design flow optimization is different ASIC design. The ASIC vendor has created a library of cells and functions that the designer can use without needing to know precisely how. Hardware Description Language HDL Verilog Professional Verilog Coding for Synthesis Verification Techniques FPGA Architectures Digital System Design with Xilinx FPGAs ASIC Digital Design Flow from Verilog to the actual Chip Synthesis Algorithms Power Dissipation Power Grid and Clock Design Fixed-point. FPGA flexibility and development benefits and ASIC size and power consumption advantages. The 3do Company Asic Fpga Design Cdrom Controller Pci Bus Bridge 3d Graphics Engine Note All Images Obtained From Web Graphic Card Engineering Logic.

Design is specified using HDL such as Verilog VHDL etc. As may be imagined the cost of an ASIC design is high and therefore they tend to be reserved for high volume products. ASIC requires hand instantiation of these blocks. THE MASKED GATE ARRAY ASIC An Application Specific Integrated Circuit or ASIC is a chip that can be designed by an engineer with no particular knowledge of semiconductor physics or semiconductor processes. THE MASKED GATE ARRAY ASIC An Application Specific Integrated Circuit or ASIC is a chip that can be designed by an engineer with no particular knowledge of semiconductor physics or semiconductor processes. Fpga Vs Asic Differences Between Them And Which One To Use Numato Lab Help Center.

Hardware Description Language HDL Verilog Professional Verilog Coding for Synthesis Verification Techniques FPGA Architectures Digital System Design with Xilinx FPGAs ASIC Digital Design Flow from Verilog to the actual Chip Synthesis Algorithms Power Dissipation Power Grid and Clock Design Fixed-point. Syllabus Regulation 2013 Click Here To Download. This application note gives some guidelines for efficient FPGA implementation of their designs. To give the student an understanding of issues and tools related to ASICFPGA design and implementation including timing performance and power optimization verification and manufacturing test. It involves about seven different stages from system specification to tape out for fabrication. Fpga Vs Asic Design Flow Ppt Video Online Download.

The significant difference between ASIC and FPGA design flow is that the design flow for ASICs is a far more complex and rigorous design-intensive process. SoC ASIC and Complex FPGA Design Digital design complexity tackled with process and metrics. One can get started with FPGA development for as low as USD 30. The significant difference between ASIC and FPGA design flow is that the design flow for ASICs is a far more complex and rigorous design-intensive process. In addition to the non-recurring engineering NRE and mask costs development costs are increasing due to design complexity. Fpga Vs Asic Differences Between Them And Which One To Use Numato Lab Help Center.